xdc约束优先级,推荐的约束规范,实际的工程约束

xdc优先级

- 在xdc文件中,按约束的先后顺序依次被执行,因此,针对同一个时钟的不同约束,只有最后一条约束生效。虽然执行顺序是从前到后,但不同约束语句的优先级却并不相同,就像四则运算一样,+-x÷都是按照从左到右的顺序执行,但x÷的优先级比+-要高。

约束优先级的总体原则

- 对于XDC约束,首先考虑约束的类型,根据时序例外的优先级进行排序;在时序例外的优先级一致的情况下,再考虑约束的对象,约束的越精细,则优先级越高;接着再考虑路径约束的优先级,-from > -to > -through;如果以上均无法区分,最后再根据约束的先后顺序进行判断,针对同一个时钟的不同约束,只有最后一条约束语句生效。

#时序例外的优先级 - 时序例外的优先级从高到低为:

- Clock Groups (set_clock_groups)

- False Path (set_false_path)

- Maximum Delay Path (set_max_delay) and Minimum Delay Path (set_min_delay)

- Multicycle Paths (set_multicycle_path)

- set_bus_skew约束并不影响上述优先级且不与上述约束冲突。原因在于set_bus_skew并不是某条路径上的约束,而是路径与路径之间的约束。

约束对象的优先级

- 对于同样的约束,定义的越精细,优先级越高。

- 各对象的约束优先级从高到低为:

- ports->pins->cells

- clocks

路径声明的优先级

- 路径声明的优先级从高到低为:

- -from -through -to

- -from -to

- -from -through

- -from

- -through -to

- -to

- -through

具体举例

Example 1

set_max_delay 12 -from [get_clocks clk1] -to [get_clocks clk2]

set_max_delay 15 -from [get_clocks clk1]

- 在该约束中,第一条语句和第二条语句均为对最大延时的约束,且约束对象均为"clocks",又由于第一条约束的"-from -to"的优先级高于第二条语句的"-from",所以第一条约束会覆盖第二条约束。

Example 2

set_max_delay 12 -from [get_cells inst0] -to [get_cells inst1]

set_max_delay 15 -from [get_clocks clk1] -through [get_pins hier0/p0] -to

[get_cells inst1]

- 在该约束中,第一条语句和第二条语句均为对最大延时的约束,第一条语句是对"cells"的约束,第二条语句是对"clocks"的约束,故第一条语句的优先级高于第二条语句。虽然在路径优先级方面第一条约束的"-from -to"低于第二条语句的"-from -through -to",但因为优先考虑对象,再考虑路径的总体原则,故第一条约束会覆盖第二条约束。

Example 3

set_max_delay 4 -through [get_pins inst0/I0]

set_max_delay 5 -through [get_pins inst0/I0] -through [get_pins inst1/I3]

- 在该约束中,第一条语句与第二条语句均为对最大延迟的约束,对象也均是"pin",约束路径也都使用了"-through",故两者的优先级一致,两条语句均为存在,且会合并为更为严苛的约束条件,合并后的约束如下:

set_max_delay 4 -through [get_pins inst0/I0] -through [get_pins inst1/I3]

约束规范

xdc推荐约束顺序

- 无论是为设计使用一个还是多个XDC文件,都按以下顺序组织约束文件。

- 首先先对时钟进行约束,必须先创建时钟,然后才能将它们用于任何后续约束。 声明之前对时钟的任何引用都会导致错误,并忽略相应的约束。具体包括基本时钟,衍生时钟,时钟组,时钟抖动,输入输出延时等

- 接着对时序例外进行约束,包括伪路径,多轴器路径,最大最小延迟等。

- 对于物理管脚约束,包括管脚位置与管脚电平约束等,既可以放在时序约束前,也可以放在时序约束后具体可根据个人习惯进行。

## Timing Assertions Section

# Primary clocks

# Virtual clocks

# Generated clocks

# Clock Groups

# Bus Skew constraints

# Input and output delay constraints

## Timing Exceptions Section

# False Paths

# Max Delay / Min Delay

# Multicycle Paths

# Case Analysis

# Disable Timing

## Physical Constraints Section

# located anywhere in the file, preferably before or after the timing constraints

# or stored in a separate constraint file

约束文件顺序

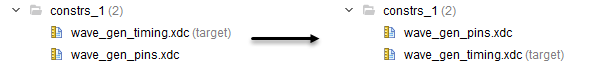

- 约束文件的顺序很重要。 您必须确保每个文件中的约束不依赖于另一个文件的约束。 如果两个约束文件具有相互依赖关系,则必须将它们手动合并到一个包含正确序列的文件中,或者将文件分成几个单独的文件并正确排序。

- 在没有任何IP的项目流程中,所有约束都位于约束集中。 默认情况下,Vivado IDE中显示的XDC文件(或Tcl脚本)的顺序定义了将elaborated design或synthesized design加载到内存时工具使用的读取顺序。 首先读取列表顶部的文件,最后读取底部的文件。您只需在IDE中选择文件并将其移动到列表中的所需位置即可更改顺序。

- 在许多IP内核中会随附一个或多个XDC文件。在RTL项目中生成此类IP内核时,还会在各种设计编译步骤中使用其XDC文件。默认情况下,会在用户XDC文件之前读入IP XDC文件。

- 对于属于同一组的用户XDC(或Tcl)文件,Vivado IDE中显示的相对顺序决定了它们的读取顺序;而对于对于属于同一组的IP XDC文件,顺序由IP内核的导入或创建顺序确定, 创建项目后,无法更改此顺序。

实际的工程约束

- 以上的前几个章节,都是时序约束的教科书版本式的流程。但在实际的项目工程中,我们基本遵循之前所讲到的约束思路,但仍存在一些小差异:

- 首先是虚拟时钟,这个约束在平时的工程中基本不会用到,像需要设置虚拟时钟的场景,我们也都是通过设计来保证时序收敛,设置虚拟时钟的意义不大。

- 第二就是output delay,在FPGA的最后一级寄存器到输出的路径上,往往都使用了IOB,也就是IO block,因此最后一级寄存器的位置是固定的,从buffer到pad的走线延时是确定的。在这种情况下,是否满足时序要求完全取决于设计,做约束只是验证一下看看时序是否收敛。所以也基本不做。但是input delay是需要的,因为这是上一级器件输出的时序关系。

- 第三个就是多周期路径,我们讲了那么多多周期路径的应用场景,但实际我们是根据Timing report来进行约束的,即便那几种场景都存在,但如果Timing report中没有提示任何的时序 warning,我们往往也不会去添加约束。

- 第四个就是在设置了多周期后,如果还是提示Intra-Clocks Paths的setup time不过,那就要看下程序,是否写的不规范,是否是程序编写上,在一个时钟周期内做了过多的操作,可考虑进行逻辑功能的拆分。

参考:

1.FPGA时序约束理论篇之xdc约束优先级-Author:猫叔

2. 《Xilinx FPGA权威设计指南--基于Vivado2018集成开发环境》,何宾,电子工业出版社