功能仿真,仿真原理

功能仿真是FPGA项目开发中重要的一环,它是确保HDL设计代码在功能上准确无误的重要方法。

串行模仿并行思路

- FPGA中的电路都是并发执行的,因此HDL语言的本质也是并行的,并且硬件电路是无时无刻不在工作的。可FPGA的功能仿真是基于PC机上的相关软件仿真环境的,而PC机上软件的执行思路都是串行的,并且PC机每秒的运算次数是有限的。故如何使用串行进行并行仿真便是第一个需要解决的问题。

- 串行模仿并行主要分为两种情况:独立的并行电路和有关联的并行电路。

仿真独立的并行电路

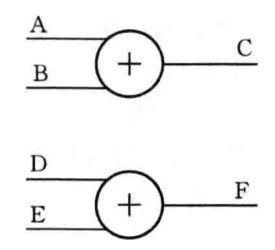

- 若并行的电路之间是相互独立的,那么此时,同时开始做N件事和做完一件事再开始下一件事从结果上来看是完全一样的。例如加法器1的输人是A和B,输出是C,加法器2的输人是D、E,输出是F,如下图所示

。

。 - 此时无论是同时计算两个加法器的输出结果还是按任意顺序逐个计算两个加法器的输出结果,最终得到的答案都会是一样的。因此这种情况下串行可以比较轻松地模拟并行。

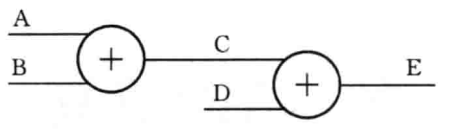

##仿真有关联的并行电路 - 若并行的电路之间不是相互独立的,那么此时,情况就不那么简单了。例如,加法器1的输人是A和B,输出是C,加法器2的输人是C、D,输出是E,如下所示。

- 这个时候,由于模拟环境会保留电路上一次模拟后的结果,所以先计算加法器1还是加法器2,得到的结果是不同的,并且此时并行的模拟思路如果只做一次,也无法给出正确地结果。因此这种情况下,串行要想正确地模拟并行,需要遵循正确地执行顺序。所以,为了配合得出正确地仿真结果,在串行子语句体中最好能够严格按照数字信号传递的方向书写代码。

有限模仿无限的思路

- 硬件电路只要一上电,就会持续不断地工作,永不停歇,因为现实中的电信号时间一上都是连续的。而软件的计算都是离散的,即使令仿真的时间间隔趋近于无穷小,这样虽然可以使真情况无限逼近真实情况,但是仍不能完全代替真实情况,并且从计算量上来看,也是无法完成的。

组合逻辑仿真原理

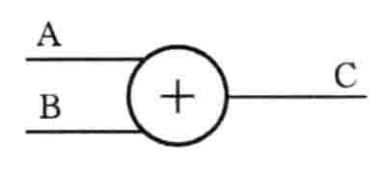

- 下例仍以一个加法器来进行分析,设加法器的输入为A和B,输出为C。

- 若一开始,令A等于5,B等于3,那么C自然应该等于8。若这种情况持续了10秒钟,那么,在这10秒钟之内,由于A和B的值都没有改变,虽然加法器电路在一直工作,而且也经过了无数次的加法运算,可是由于每次计算出的C值都为8,因此输出也一直没有改变。如果在这之后,A的值变为7,那么加法器的输出C会迅速变为10,并且此后C的值会一直保持下去,直到A或B的下一次变化到来,C才有可能中改变。

- 虽然硬件电路无时无刻不在进行运算,但是,只有那些可能会改变输出的运算才是最重要的,只要能够捕捉住这些关键时刻,就可以完全模拟出真实的情况。因此,利用这一思路,就可以在FPGA中用有限来模拟无限了。

时序逻辑仿真原理

- 时序逻辑中最重要的就是寄存器。以一个最基本的上升沿敏感的寄存器为例来讨论,它有三个最重要的端口,分别是两个输人端口clk.D,-个输出端口Q。它的功能可以描述为无论输人端口D的值怎么变化,当且仅当clk的上升沿到来的时刻,更新输出端口Q的值为此时输人端口D的值。此后端口Q的值将会保持下去,直到下一次clk的上升沿到来才有可能更新。

- 因此,虽然寄存器内部的电路是一直工作的,而且随着D值的变化,寄存器内部的部分电路的值也是不断在变化的,可是由于在任意两个连续的clk上升沿期间,Q值绝对不会变化,所以可以仅保留clk的上升沿时刻作为关键时刻,来化无限为有限,从而得出正确地仿真结果。

仿真基本概念

仿真零时刻

- 一般来说,默认仿真最开始的时刻就是仿真0时刻,也就是点击开始仿真按钮的那一瞬间。请注意,仿真0时刻是一个相对值,而不是一个绝对的值,这类似于电压中0电势的定义,重要的不是认定什么时候才是0时刻,而是需要确定这么一个时刻,好让所有其他的时刻都可以此时刻为基准来进行描述。

"边沿对边沿"判定

- 对于时序逻辑的仿真来说,当出现时钟信号的有效边沿时(一般是上升沿),对应数据信号的逻辑电平会被传递到触发器的输出端,故时钟信号与数据信号是一种"边沿对边沿"的关系。那么,当时钟信号的有效边沿正好也对应到了数据的边沿,此时的数据信号到底应该判断为逻辑0还是逻辑1呢,下面给出判断规则。

- 如果时钟边沿发生在t时刻,那么令Δ为正无穷小,则被寄存器传递的数据逻辑电平所处的时刻为t-Δ时刻。对于时钟有效边沿与数据信号的四种对应关系列举如下:

- 时钟有效边沿对应数据逻辑1电平,则t-Δ时刻的数据线上仍为逻辑1电平,这种情况下寄存器输出逻辑1电平至其输出端;

- 时钟有效边沿对应数据逻辑0电平,则t-Δ时刻的数据线上仍为逻辑0电平,这种情况下寄存器输出逻辑0电平至其输出端;

- 时钟有效边沿正好对齐数据线上从逻辑1到逻辑0电平的跳变,则t-Δ时刻的数据线上应该为逻辑1电平,这种情况下寄存器输出逻辑1电平至其输出端;

- 时钟有效边沿正好对齐数据线上从逻辑0到逻辑1电平的跳变,则t-Δ时刻的数据线上应该为逻辑0电平,这种情况下寄存器输出逻辑0电平至其输出端;

- 需要注意!,在真实电路中,如果时钟边沿发生在t时刻,则寄存器A输出更新的时刻应为t+Δ时刻。在不考虑时钟路径延迟的情况下,寄存器B的时钟有效边沿时刻为t时刻,对应的数据逻辑电平其实还是寄存器A在t时刻输出的逻辑电平,因此数据才能在移位寄存器中逐个传递下去。可是由于功能仿真中不考虑延迟,所以寄存器A输出的更新时刻仍为t时刻,因此在这个时候,为了确定寄存器B的输出,就必须追溯到t-0时刻。

观察波形的具体操作

- 波形缩放:使用

Ctrl+鼠标滚轮,即可在Vivado中缩放仿真波形,方便设计者从不同尺度观测仿真波形。 - 界面移动:拖动界面的拖动框,可移动波形图,或可使用

鼠标滚轮,上下移动波形;Shift+鼠标滚轮,左右移动波形。 - 总线观察:用户定义的总线型信号,在仿真波形中也会以总线形式存在。可点击展开总线,观测每一条总线的具体数值;也可以"右键波形 -> Radix",选择对应的数值进制以及是否带有符号位,或者选择"Waveform Style",设置波形为模拟波形查看或数字波形查看。

- 添加时钟标记:点击

Add Market图标,添加时间标尺,可通过点击拖动的方式移动时间标尺的位置,还可在时间标尺处读取到标尺位置的具体时间。 - 边沿查找:选中需要观察的波形信号,使用左右方向键,便可自动移动标尺位置,标尺会自动吸附在信号的边沿上,在各个上升、下降沿之间移动。

参考:

《FPGA之道》,狄超,刘萌著,西安交通大学出版社,6.1章